Overview

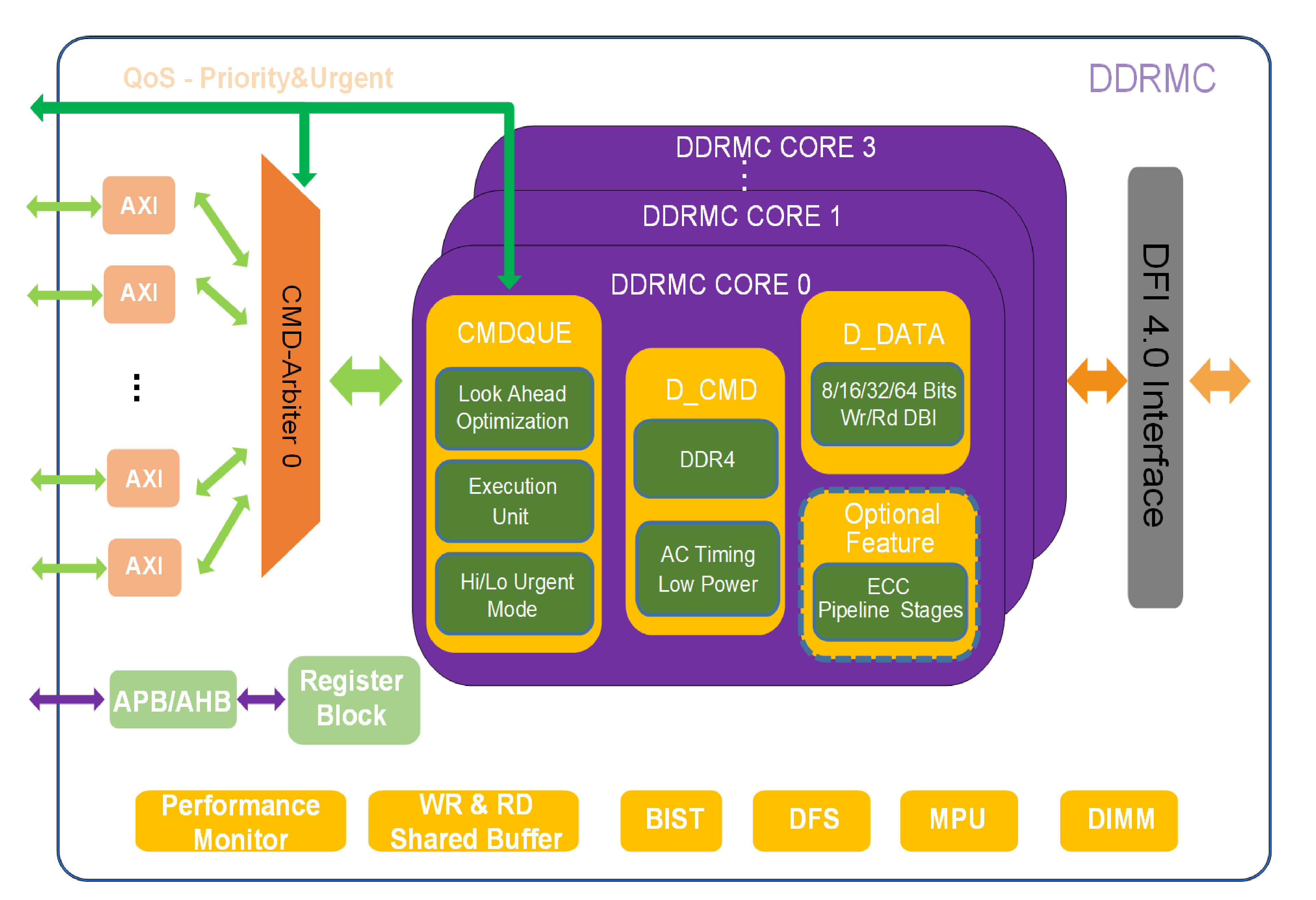

With sophisticated architecture and advanced technology, KNiulink provide DDR4 IP solution with high performance and low power. In advanced process nodes, KNiulink could offer both controller and PHY IPs. In architecture, it supports Multiport AMBA AXI interface, configurable port number and support asynchronous or synchronous AXI port. For PHY interface, it will integrate DFI compatible design. One de-skew PLL is embedded inside the PHY to improve jitter performance.

Highlights

- • Compatible with DDR4 up to 3200Mbps

- • AXI compliant multi-ports, and data width, FIFO depth, command queue depth configurable

- • DFI compliant interface between controller and PHY

- • Support ECC (error correcting code)

- • Automatic temperature monitor and refresh rate adjust

- • Support CA, write, read VREF eye training and per-bit training, write leveling training

- • Support Inline BIST and SIPI/LFSR/USER patterns

- • Support DDRPHY loopback test for high speed test

- • Fully PINMUX easy for PKG/PCB routing

- • Support mask write, write/read DBI

- • Support Hardware based DDR frequency switch (DFS), and DFI programmable with frequency, trade-off latency and power

Deliverables

- - Datasheet (Including Integration Guideline, Interface PINs, clock and reset description, all training flows etc.) (DDRMC & DDRPHY)

- - Register Map files (register address and function description), timing calculation sheet (DDRMC & DDRPHY)

- - Timing lib/db, Layout Frame (.LEF) (DDRPHY)

- - Encrypted RTL and Netlist, SPEF/SDF (DDRPHY)

- - Top Level GDS (DDRPHY)

- - RTL Code & SDC Constraints (DDRMC)

- - Verification environment and cases (testbench, DDRIO Verilog model, initial flow, training flow, bandwidth access, DFT pattern etc. (DDRMC & DDRPHY)

Highlights

- • Compatible with DDR4 up to 3200Mbps

- • AXI compliant multi-ports, and data width, FIFO depth, command queue depth configurable

- • DFI compliant interface between controller and PHY

- • Support ECC (error correcting code)

- • Automatic temperature monitor and refresh rate adjust

- • Support CA, write, read VREF eye training and per-bit training, write leveling training

- • Support Inline BIST and SIPI/LFSR/USER patterns

- • Support DDRPHY loopback test for high speed test

- • Fully PINMUX easy for PKG/PCB routing

- • Support mask write, write/read DBI

- • Support Hardware based DDR frequency switch (DFS), and DFI programmable with frequency, trade-off latency and power

Applications

-

PC

-

Server

-

Workstations

-

Cell Phone

-

Storage Devices