Overview

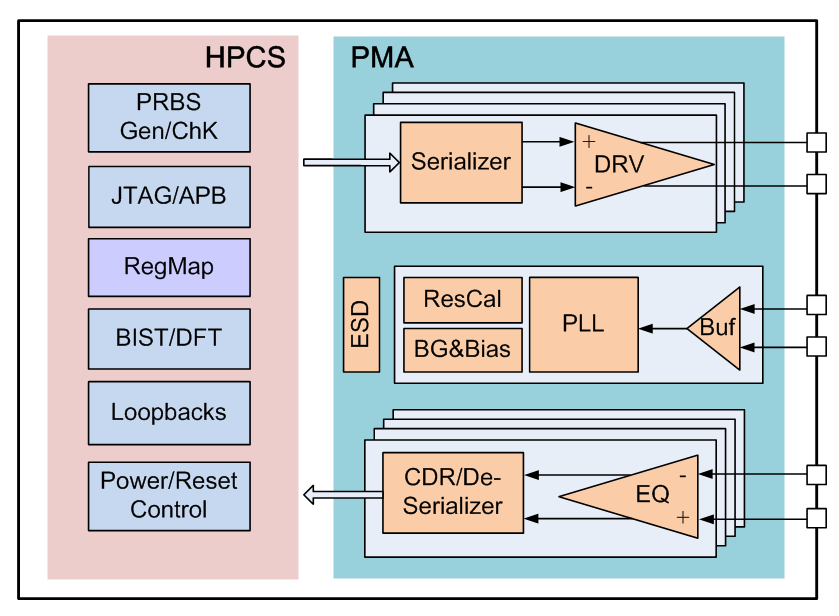

With sophisticated architecture and advanced technology, KNiulink multi-mode transceiver IP with PMA and PCS layer is designed for low power and high performance application. It is highly configurable and can be tightly integrated with the user logic or SOC resources; it can support a wide variety of serial data transmission protocols with link rate up to 25/28/32Gbps.

Highlights

- • 4 Channels per Quad

- • Data rate up to 25/28/32Gbps

- • Shared Quad LC-PLL for high performance

- • Independent Ring-PLL of each channel for clock flexibility

- • Support the following protocols: CEI-25G/28G/PCIE4.0/JESD204C/ USB3.1/10G-KR/SATA3/DP1.4

- • Digitally-control-impedance termination resistors

- • Configurable TX output differential voltage swing

- • Built-in TX De-Emphasis

- • RX Built-in CTLE and Decision Feedback Equalization

- • Multiple Loop Back, BIST, and Analog DC Testing

- • Support RX Built-in Eye Opening Monitor

- • Support Boundary Scan Interface for Serial link, compliant with IEEE 1149.6-2003/ 1149.1-2001

- • BIST (PRBS-7, PRBS-15, PRBS-23, PRBS-31, fixed-pattern) generator and checker

- • Low Power Consumption

- • Supports Flip-Chip package

Deliverables

- - GDSII&CDL Netlist

- - Verilog Model

- - LEF Layout Abstract(.LEF)

- - Liberty Timing Models(.lib)

- - Verify Results

- - Specification

- - Datasheet

- - Integration Guideline

- - Evaluation Plan

- - Leading support for package design, SI&PI modeling and production test development

Highlights

- • 4 Channels per Quad

- • Data rate up to 25/28/32Gbps

- • Shared Quad LC-PLL for high performance

- • Independent Ring-PLL of each channel for clock flexibility

- • Support the following protocols: CEI-25G/28G/PCIE4.0/JESD204C/ USB3.1/10G-KR/SATA3/DP1.4

- • Digitally-control-impedance termination resistors

- • Configurable TX output differential voltage swing

- • Built-in TX De-Emphasis

- • RX Built-in CTLE and Decision Feedback Equalization

- • Multiple Loop Back, BIST, and Analog DC Testing

- • Support RX Built-in Eye Opening Monitor

- • Support Boundary Scan Interface for Serial link, compliant with IEEE 1149.6-2003/ 1149.1-2001

- • BIST (PRBS-7, PRBS-15, PRBS-23, PRBS-31, fixed-pattern) generator and checker

- • Low Power Consumption

- • Supports Flip-Chip package

Applications

-

FPGA System

-

SOC System

-

Communication System