Overview

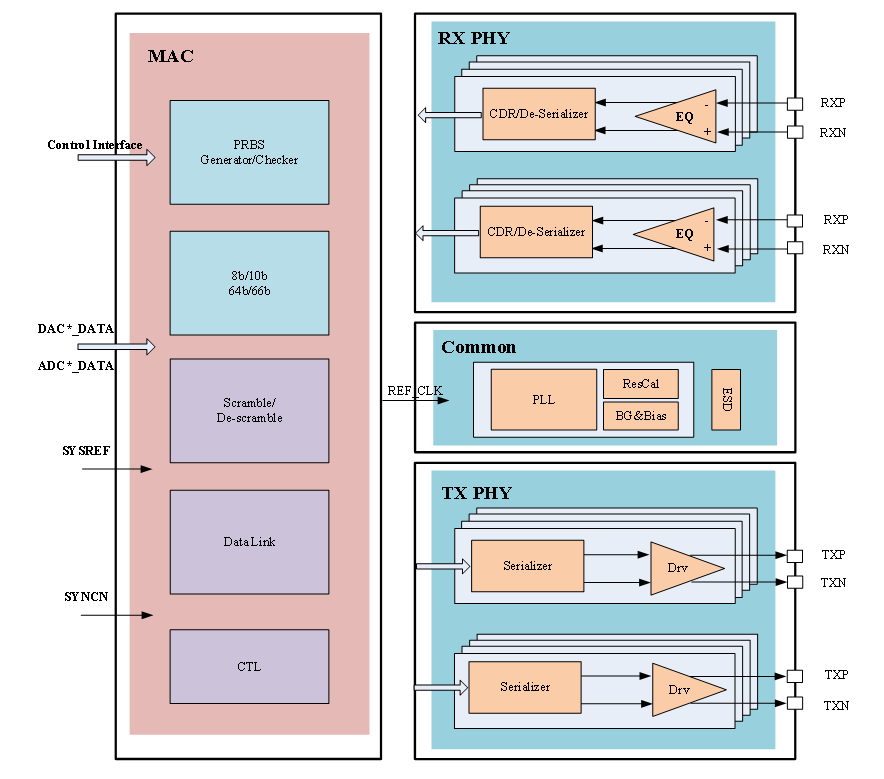

With sophisticated architecture and advanced technology, JESD204B /204C IP with PHY and MAC layer is designed for low power and high performance application. It is fully compatible with JESD204B/204C specification, and supports link rate up to 25Gbps per lane.

Take JESD204B TX IP as an example, which assembles the parallel data from the ADCs into frames and uses 8b/10b encoding, as well as optional scrambling, to form serial output data. For the MAC side, it has the transport layer, which handles packing the data into the JESD204B frames. Besides, the data link layer is responsible for the low level functions of passing data across the link. For the PMA side, it has four lanes and a common block.

Highlights

- • X4/X8 Lane Mode, support up to 25Gbps (per lane)

- • Shared common PLL based architecture

- • Digitally-control-impedance termination resistors and On-chip resistance calibration

- • Configurable TX output differential voltage swing

- • Built-in TX De-Emphasis

- • RX Built-in Decision Feedback Equalization

- • PLL Frequency Lock detection

- • Support BIST, and Analog DC Testing

- • Fully Compatible with JESD204B/204C standard release

- • Supports Subclasses 0, 1

- • Serial lane alignment and monitoring

- • Lane synchronization

- • Deterministic latency support

- • PRBS (PRBS-7/PRBS-15/PRBS-23/PRBS-31) generator and checker

- • Support data polarity inversion

- • 8b/10b and 64b/66b encoding

- • Optional Scrambling/De-Scrambling

- • Register control through APB interface

Deliverables

- - GDSII&CDL Netlist

- - Verilog Model

- - LEF Layout Abstract(.LEF)

- - Liberty Timing Models(.lib)

- - Verify Results

- - Specification

- - Datasheet

- - Integration Guideline

- - Evaluation Plan

- - Leading support for package design, SI&PI modeling and production test development

Highlights

- • X4/X8 Lane Mode, support up to 25Gbps (per lane)

- • Shared common PLL based architecture

- • Digitally-control-impedance termination resistors and On-chip resistance calibration

- • Configurable TX output differential voltage swing

- • Built-in TX De-Emphasis

- • RX Built-in Decision Feedback Equalization

- • PLL Frequency Lock detection

- • Support BIST, and Analog DC Testing

- • Fully Compatible with JESD204B/204C standard release

- • Supports Subclasses 0, 1

- • Serial lane alignment and monitoring

- • Lane synchronization

- • Deterministic latency support

- • PRBS (PRBS-7/PRBS-15/PRBS-23/PRBS-31) generator and checker

- • Support data polarity inversion

- • 8b/10b and 64b/66b encoding

- • Optional Scrambling/De-Scrambling

- • Register control through APB interface

Applications

-

High Speed ADC/DAC

-

5G RF Transceiver

-

Base Station