Overview

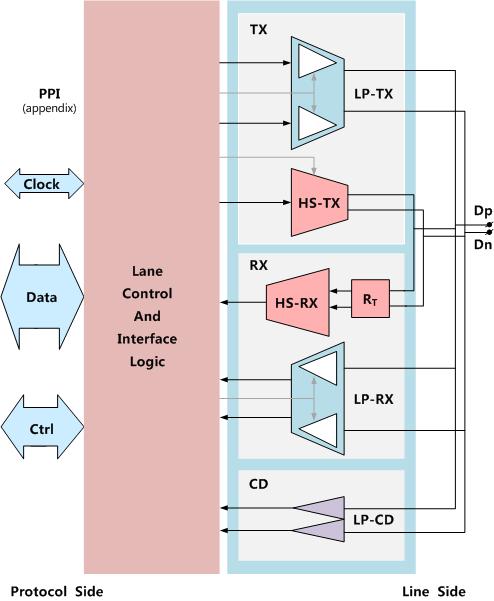

This MIPI D-PHY IP is designed to compliant with the MIPI D-PHY v1.2 specifications. It is designed for low power and high-performance application. This IP supports data rate up to 2.5Gbps.

Highlights

- • Compatible with MIPI D-PHY v1.2/CSI-2 protocol

- • Up to 4-lane 2.5Gbps/ lane

- • Support 2-Lane/4-Lane Application

- • Support HS mode (80Mbps to 2.5Gbps per lane) and LP mode (up to 10Mbps)

- • Support low power mode

- • Integrated control interface logic to support PHY Protocol Interface (PPI)

- • Supports up to four virtual channel

- • Support apb interface

- • Support DFT and BIST

- • Support 2048x1536@60Hz

- • CSI-2 ECC Detection and CRC Generation

- • Special packets for frame start, frame end, line start and line end information

- • Description for the type, pixel depth and format of the application specific payload data

- • Programmable parameters

Deliverables

- - GDSII&CDL Netlist

- - Verilog Model

- - LEF Layout Abstract(.LEF)

- - Liberty Timing Models(.lib)

- - Verify Results

- - Specification

- - Datasheet

- - Integration Guideline

- - Evaluation Plan

- - Leading support for package design, SI&PI modeling and production test development

Highlights

- • Compatible with MIPI D-PHY v1.2/CSI-2 protocol

- • Up to 4-lane 2.5Gbps/ lane

- • Support 2-Lane/4-Lane Application

- • Support HS mode (80Mbps to 2.5Gbps per lane) and LP mode (up to 10Mbps)

- • Support low power mode

- • Integrated control interface logic to support PHY Protocol Interface (PPI)

- • Supports up to four virtual channel

- • Support apb interface

- • Support DFT and BIST

- • Support 2048x1536@60Hz

- • CSI-2 ECC Detection and CRC Generation

- • Special packets for frame start, frame end, line start and line end information

- • Description for the type, pixel depth and format of the application specific payload data

- • Programmable parameters

Applications

-

Video Transmission System

-

Camera Sensor