Overview

Highlights

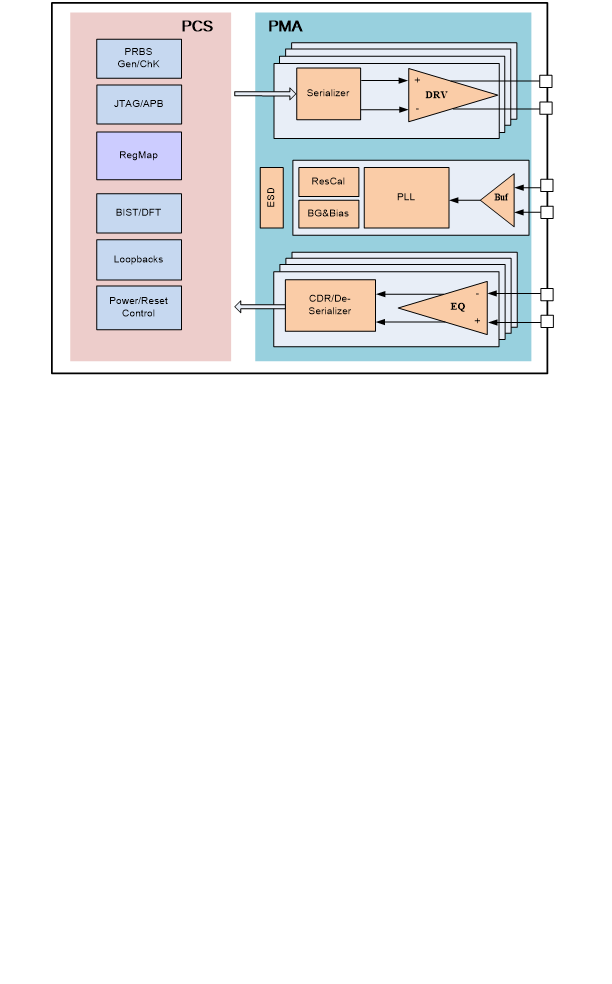

- • 8 Channels per Macro, 2.5Gbps~112Gbps with TX/RX independent; NRZ Data Rate:2.5-56Gbps PAM4 Data Rates: 56-112Gbps

- • Serialization/Deserialization interface width; PCS-User interface support 64bit in PIPE

- • Two cascaded PLLs, one LC-tank based and the other ring-oscillator based

- • Digitally-control-impedance termination resistors

- • Configurable TX output differential voltage swing

- • Built-in TX De-Emphasis

- • RX Built-in CTLE with programmable boost

- • Support Forward Clock Mode/Common Clock/CDR Assist mode

- • PLL Frequency Lock detection

- • Multiple Loop Back, BIST, and Analog DC Testing

- • Support RX Built-in Eye Opening Monitor

- • Reference clock repeater for other Quads

- • Support Boundary Scan Interface for Serial link, compliant with IEEE 1149.6-2003/ 1149.1-2001

- • BIST generator and checker

- • Support data polarity inversion

- • TX/RX status control

- • Provide the corresponding interface clocks to external SOC

- • Power on/reset sequence control

- • Support DFT

- • JTAG/APB control register access interface

- • Supports Flip-Chip package

Deliverables

- - GDSII&CDL Netlist

- - Verilog Model

- - LEF Layout Abstract(.LEF)

- - Liberty Timing Models(.lib)

- - Verify Results

- - Specification

- - Datasheet

- - Integration Guideline

- - Evaluation Plan

- - Leading support for package design, SI&PI modeling and production test development

Highlights

- • 8 Channels per Macro, 2.5Gbps~112Gbps with TX/RX independent; NRZ Data Rate:2.5-56Gbps PAM4 Data Rates: 56-112Gbps

- • Serialization/Deserialization interface width; PCS-User interface support 64bit in PIPE

- • Two cascaded PLLs, one LC-tank based and the other ring-oscillator based

- • Digitally-control-impedance termination resistors

- • Configurable TX output differential voltage swing

- • Built-in TX De-Emphasis

- • RX Built-in CTLE with programmable boost

- • Support Forward Clock Mode/Common Clock/CDR Assist mode

- • PLL Frequency Lock detection

- • Multiple Loop Back, BIST, and Analog DC Testing

- • Support RX Built-in Eye Opening Monitor

- • Reference clock repeater for other Quads

- • Support Boundary Scan Interface for Serial link, compliant with IEEE 1149.6-2003/ 1149.1-2001

- • BIST generator and checker

- • Support data polarity inversion

- • TX/RX status control

- • Provide the corresponding interface clocks to external SOC

- • Power on/reset sequence control

- • Support DFT

- • JTAG/APB control register access interface

- • Supports Flip-Chip package

Applications

-

hyperscale data centers,

-

enterprise and campus networks

-

cloud computing and networking,

-

artificial intelligence