Overview

Highlights

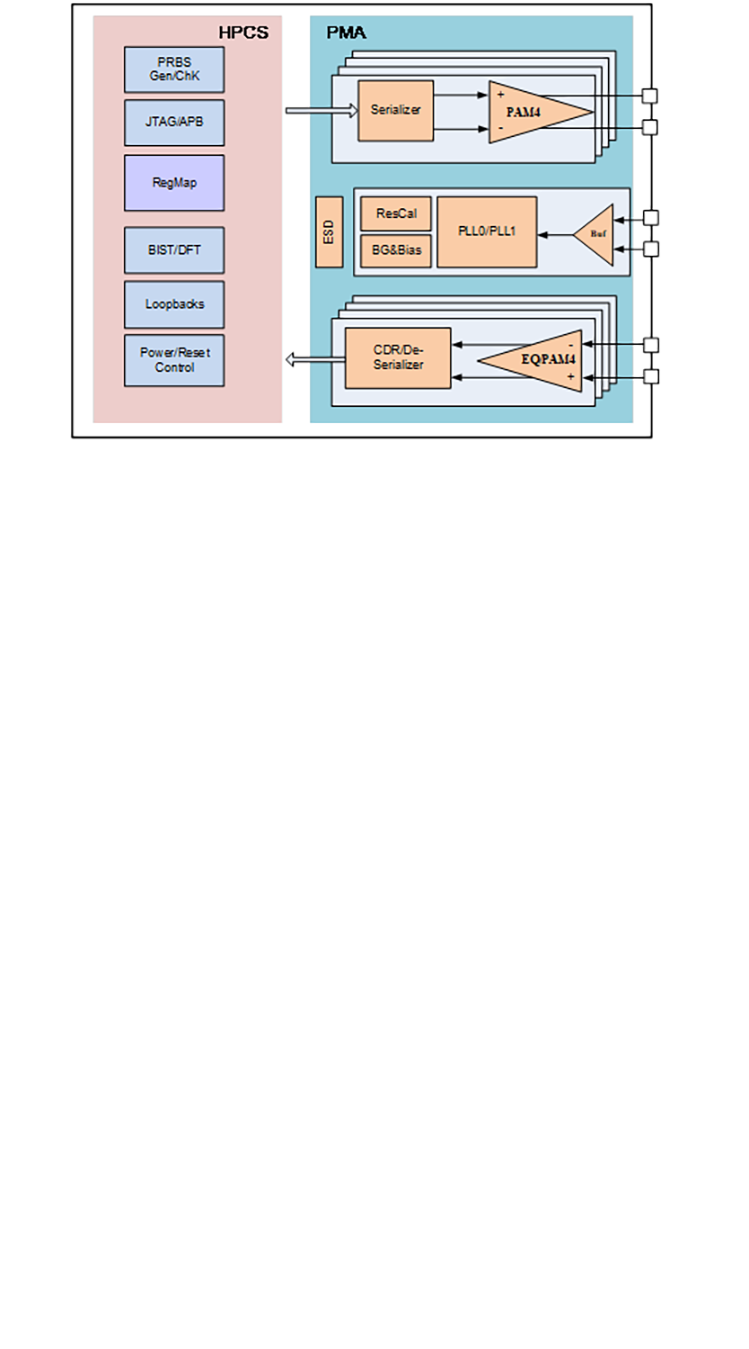

- • 4 Channels per Quad, ≤64Gbps; PAM4 support 25~64Gbps; NRZ support 2.5~32Gbps

- • Serialization/Deserialization interface width; 64/32/16bits; 64-bit parallel data path in PAM4 mode; 32-bit parallel data path in full-rate NRZ mode; 16-bit and 32-bit parallel data path widths in half-rate and quarter-rate modes

- • Four programmable transmitter and receiver configurations selectable by port by using hardware pins or registers. Facilitates fast speed switching during speed negotiation routines

- • Aggressive equalization capability to enable 64Gbps operation and legacy system upgrades

- • Feed Forward Equalization (FFE) driver equalization

- • Adaptive and configurable RX Continuous Time Linear Equalizer (CTLE), Feed Forward Equalizer (FFE) and Decision Feedback Equalizer (DFE)

- • Digital-based receiver consisting of the following: Analog Front-End (AFE) Analog-to-Digital Converter (ADC) Digital Signal Processor (DSP)

- • Digitally-control-impedance termination resistors;

- • Configurable Tx output differential voltage swing;

- • Support for manufacturing and system test

- • Generalized scan design compliant with manufacturing functional (macro) tests

- • Full-rate loopback and Built-In Self-Tests (BIST) with selectable PRBS patterns

- • Compatible with IEEE 1149.6-2003 ACJTAG

- • Supports Flip-Chip package

Deliverables

- - GDSII&CDL Netlist

- - Verilog Model

- - LEF Layout Abstract(.LEF)

- - Liberty Timing Models(.lib)

- - Verify Results

- - Specification

- - Datasheet

- - Integration Guideline

- - Evaluation Plan

- - Leading support for package design, SI&PI modeling and production test development

Highlights

- • 4 Channels per Quad, ≤64Gbps; PAM4 support 25~64Gbps; NRZ support 2.5~32Gbps

- • Serialization/Deserialization interface width; 64/32/16bits; 64-bit parallel data path in PAM4 mode; 32-bit parallel data path in full-rate NRZ mode; 16-bit and 32-bit parallel data path widths in half-rate and quarter-rate modes

- • Four programmable transmitter and receiver configurations selectable by port by using hardware pins or registers. Facilitates fast speed switching during speed negotiation routines

- • Aggressive equalization capability to enable 64Gbps operation and legacy system upgrades

- • Feed Forward Equalization (FFE) driver equalization

- • Adaptive and configurable RX Continuous Time Linear Equalizer (CTLE), Feed Forward Equalizer (FFE) and Decision Feedback Equalizer (DFE)

- • Digital-based receiver consisting of the following: Analog Front-End (AFE) Analog-to-Digital Converter (ADC) Digital Signal Processor (DSP)

- • Digitally-control-impedance termination resistors;

- • Configurable Tx output differential voltage swing;

- • Support for manufacturing and system test

- • Generalized scan design compliant with manufacturing functional (macro) tests

- • Full-rate loopback and Built-In Self-Tests (BIST) with selectable PRBS patterns

- • Compatible with IEEE 1149.6-2003 ACJTAG

- • Supports Flip-Chip package

Applications

-

400/800G Communication

-

Hyperscale Data Center

-

AI and Machine Learning