Overview

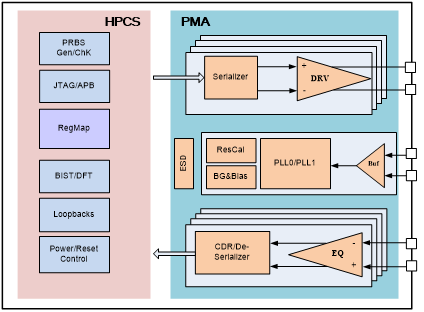

With sophisticated architecture and advanced technology, KNiulink SerDes PHY IP with PMA and PCS layer is designed for low power and high performance application. PCS layer and PMA layer include RX, TX and a common lane. The interfaces between users and IP are PIPE interface. All the control and configuration bits of the SerDes PHY IP are assigned in register map at PCS side and can be accessed through JTAG interface and register access port.

Highlights

- • Support PCI Expression Gen5 & Gen4 & Gen3 & Gen2 & Gen1

- • Configurable differential voltage swing

- • Embedded low jitter LC PLL with fixed bandwidth and output frequency

- • PLL Frequency Lock detection

- • Support termination resistance tuning

- • IEEE P1149.6-2003/P1149.1-2001(ACJTAG)

- • Support 32 Gbps PCIe Gen5, 16 Gbps PCIe Gen4, 8 Gbps PCIe Gen3, 5 Gbps PCIe Gen2 and 2.5 Gbps PCIe Gen1 Test mode

- • Support PCIe Beacon signaling

- • Advanced, built-in diagnostics including on-chip digital RX eye scope

- • Internal/external loopback

- • 8b/10b and 128b/130b encoding and decoding

- • Elastic Buffer

- • JTAG test port

- • Flip-Chip package supported

Deliverables

- - GDSII&CDL Netlist

- - Verilog Model

- - LEF Layout Abstract(.LEF)

- - Liberty Timing Models(.lib)

- - Verify Results

- - Specification

- - Datasheet

- - Integration Guideline

- - Evaluation Plan

- - Leading support for package design, SI&PI modeling and production test development

Highlights

- • Support PCI Expression Gen5 & Gen4 & Gen3 & Gen2 & Gen1

- • Configurable differential voltage swing

- • Embedded low jitter LC PLL with fixed bandwidth and output frequency

- • PLL Frequency Lock detection

- • Support termination resistance tuning

- • IEEE P1149.6-2003/P1149.1-2001(ACJTAG)

- • Support 32 Gbps PCIe Gen5, 16 Gbps PCIe Gen4, 8 Gbps PCIe Gen3, 5 Gbps PCIe Gen2 and 2.5 Gbps PCIe Gen1 Test mode

- • Support PCIe Beacon signaling

- • Advanced, built-in diagnostics including on-chip digital RX eye scope

- • Internal/external loopback

- • 8b/10b and 128b/130b encoding and decoding

- • Elastic Buffer

- • JTAG test port

- • Flip-Chip package supported

Applications

-

Data Center

-

High Performance Computing

-

Storage

-

Communications